**48** 48

49

50

52

53

56

58

59

21

62

63

71 72 73

75

76

77

91

85

30

32

33

ARTICLE IN TRESS

International Journal of Machine Tools & Manufacture XX (2003) XXX-XXX

# Fine grinding of silicon wafers: a mathematical model for grinding marks

S. Chidambaram<sup>a</sup>, Z.J. Pei<sup>a,\*</sup>, S. Kassir<sup>b</sup>

<sup>a</sup> Department of Industrial and Manufacturing Systems Engineering, Kansas State University, 237 Durland Hall, Manhattan, KS 66506-5101,

USA

<sup>b</sup> Strasbaugh, Inc., 825 Buckley Road, San Luis Obispo, CA 93401, USA

Received 7 April 2003

## Abstract

The majority of today's integrated circuits are constructed on silicon wafers. Fine-grinding process has great potential to improve wafer quality at a low cost. Three papers on fine grinding were previously published in this journal [Microchip Fabrication, McGraw-Hill, New York, 2000; Silicon Machining Symposium, American Society For Precision Engineering, St. Louis, Missouri, April, 1998; East Bay Business Times, February 12, 2002]. The first paper discussed its uniqueness and special requirements. The second one presented the results of a designed experimental investigation. The third paper developed a mathematical model for the chuck shape, addressing one of the technical barriers that have hindered the widespread application of this technology: difficulty and uncertainty in chuck preparation. As a follow up, this paper addresses another technical barrier: lack of understanding on grinding marks. A mathematical model to predict the locus of the grinding lines and the distance between two adjacent grinding lines is first developed. With the developed model, the relationships between grinding marks and various process parameters (wheel rotational speed, chuck rotational speed, and wheel diameter) are then discussed. Finally, results of pilot experiments to verify the model are discussed.

© 2003 Published by Elsevier Ltd.

Keywords: Grinding; Machining; Modeling; Semiconductor material; Silicon wafer

## 1. Introduction

## 1.1. Silicon wafers and their manufacturing processes

Integrated circuits (ICs) are built on semiconductor wafers. Over 90% of semiconductor wafers are silicon [1]. About 150 million silicon wafers of different sizes are manufactured each year worldwide [2]. In 2000, the worldwide revenue generated by silicon wafers was \$ 7.5 billion [3]. Semiconductor devices built on these wafers generated \$ 200 billion in revenues [4].

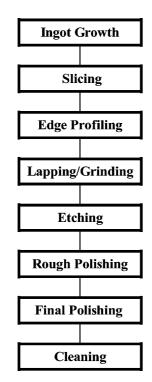

Manufacturing of silicon wafers starts with growth of silicon ingots. A sequence of processes is needed to turn an ingot into wafers. As shown in Fig. 1, this typically consists of the following processes [5–8]:

0890-6955/\$ - see front matter @ 2003 Published by Elsevier Ltd. doi:10.1016/S0890-6955(03)00187-1

- 1. slicing, to slice a silicon ingot into wafers of thin disk shape; 90

- edge profiling or chamfering, to chamfer the peripheral edge portion of the wafer;

- 3. flattening (lapping or grinding), to achieve a high degree of parallelism and flatness of the wafer; 96

- 4. etching, to chemically remove the damage induced by slicing and flattening without introducing further mechanical damage;

- 5. rough polishing, to obtain a mirror surface on the wafer;

- 6. fine polishing, to obtain final mirror surface; and

- 7. cleaning, to remove the polishing agent or dust particles from the wafer surface.

## 1.2. Wafer flatness

As the starting materials for fabrication of most ICs, <sup>110</sup> silicon wafers must be very flat in order to print circuits <sup>111</sup> on them by lithographic processes. Wafer flatness <sup>112</sup>

105

108

108

<sup>\*</sup> Corresponding author. Tel.: +1-785-532-3436; fax: +1-785-532-3738.

E-mail address: zpei@ksu.edu (Z.J. Pei).

364

2

S. Chidambaram et al. / International Journal of Machine Tools & Manufacture XX (2003) XXX-XXX

570

117

118

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

2

Fig. 1. Traditional process flow for manufacturing of silicon wafers.

directly impacts device line-width capability, process 113 latitude, yield, and throughput [9,10]. Continuing 114 reduction in feature sizes demands increasingly flatter wafers [11]. 116

Wafer flatness can be characterized in terms of a global or site parameter. A frequently used parameter to measure site flatness is SBIR (site flatness, back reference surface, ideal reference plane, range) [12]. It is the sum of the maximum positive and negative deviations of the surface in a certain area of the wafer from a theoretical reference plane that is approximately parallel to the back surface of the wafer and intersects the front surface at the center of the area. Typical size of the area is 20  $\times$  20 mm<sup>2</sup> for ordinary wafers and 30  $\times$  35 mm<sup>2</sup> for advanced applications.

For wafers manufactured by a traditional process flow, only a small percentage meet tight flatness specifications. The wafers that do not meet the specifications are often rejected, causing high yield-loss. Silicon wafer manufacturers are under tremendous pressure to develop alternative process flows or new processes to produce flatter wafers at an affordable cost.

#### 1.3. Approaches to flatness improvement 135

Several approaches have been proposed to improve 136 flatness. The first approach is double-side polishing 137 [6,13]. If operating properly, it is capable of achieving 138 superior flatness. It has become the standard polishing 139 operation for 300 mm wafers. However, its application 140 to wafers with diameter of 200 mm and less has stalled. 141

The primary reason is that double-side polishing creates mirror finish surfaces on both front side and backside of the wafer. This causes problems in IC fabs. Respective sensors of processing equipment cannot distinguish the front side from the backside. Furthermore, wafers with both sides mirror polished tend to slip out during handling process [6].

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

161

179

The second approach is called PACE, plasma-assistant chemical etching [9]. The PACE operation requires point-by-point thickness profile data that typically cover several thousand discrete positions on the front surface of the wafer. The PACE machine removes the material at each position on the wafer according to the profile data. Excellent flatness has been reported with PACE. The major drawbacks of this approach are high capital investment and low throughput.

Another approach is etched-wafer fine grinding [14]. 158 Fine grinding is used to partially replace the rough-pol-159 ishing process, addressing two problems associated with 160 the traditional process flow: poor flatness and high cost.

Fine grinding of etched wafers first appeared in public 162 domain through the US patent by Vandamme et al. [14]. 163 Pei and Strasbaugh [15] reported an experimental study 164 on the effects of grinding wheels, process parameters, 165 and coolant. They also presented results of a designed 166 experiment [16] in which three-factor, two-level full fac-167 torial design was used to reveal the main and interaction 168 effects of three process parameters (wheel speed, chuck 169 speed, and feedrate) on process outputs (grinding force, 170 spindle motor current, cycle time, surface roughness, and 171 grinding marks). Chidambaram et al. [17] developed a 172 mathematical model to predict the relations between the 173 chuck shape and the setup parameters, aiming to over-174 come one of the technical barriers that have hindered the 175 widespread application of fine grinding: difficulty and 176 uncertainty of chuck preparation. Oh et al. [18] reported 177 a study on damage induced by fine grinding. 178

## 1.4. Benefits of fine grinding

Generally, a wet etching process can negatively affect 180 flatness [19], and extended polishing (of single-side, 181 wax-mounting type) can deteriorate flatness [14]. 182 Because fine grinding will improve the flatness of etched 183 wafers and reduce the removal amount of rough pol-184 ishing by 25-50%, the flatness of polished wafers can 185 be improved. Furthermore, fine grinding can reduce 186 manufacturing costs due to the following reasons: (1) it 187 reduces polishing removal amount and cuts down the 188 time of the expensive polishing operation, (2) it 189 improves flatness and lowers the yield-loss, and (3) it 190 grinds wafers to a uniform thickness and eliminates the 191 sorting operation for production lines that polish mul-192 tiple wafers simultaneously. If multiple wafers with dif-193 ferent thickness are mounted on the same polishing 194 plate, these wafers will not have good flatness after pol-195 ishing. Without fine grinding, the thickness variation among etched wafers is quite large; hence, a sorting operation is often needed, adding extra cost.

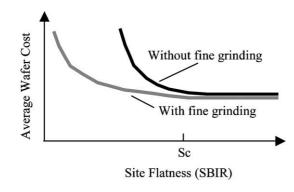

Introducing fine-grinding step requires capital investment (purchasing and installation of grinder) and additional costs (utilities, consumables, and labor). Furthermore, a cleaning step is usually required after fine grinding (before polishing). Adoption of fine grinding into a production line makes economic sense only if the cost reduction is greater than the added cost. As illustrated in Fig. 2, the economic benefit of fine grinding will become more prominent when the flatness specification becomes tighter (say, SBIR < Sc).

Although fine grinding has been implemented in some production lines with good results, it cannot be economi-210 cally justified for many other lines. To gain widespread application, the cost curve with fine grinding in Fig. 2 has to be much lower. This cost curve can be lowered 213 by further reducing the polishing amount, because the 214 smaller the polishing amount, the shorter the polishing time and the less expensive the polishing step. Furthermore, the smaller the polishing amount, the less the 217 degradation of flatness and the lower the yield-loss. 218 However, further reduction of polishing amount becomes very difficult due to the lack of fundamental 220 understanding about some issues in fine grinding. One such issue is the grinding marks left on the wafer surface 222 after fine grinding.

## 1.5. Grinding marks

196

197

198

199

200

201

202

203

204

205

206

207

208

209

211

212

216

219

221

223

224

225

226

227

228

230

231

232

233

234

235

573

578

586

2

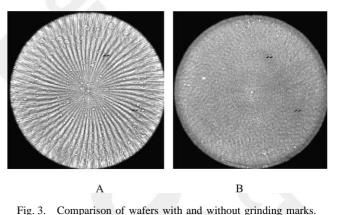

Fig. 3 shows pictures of two silicon wafers after fine grinding and polishing. Wafer B is good since no patterns are visible, but wafer A is not acceptable due to visible grinding marks. One approach to correct wafer A is to keep polishing it until all grinding marks are gone. This will lengthen the polishing time, increase manufacturing costs, and deteriorate flatness. A better approach is to optimize the fine-grinding process so that grinding marks can be removed with minimum polishing. The success of the latter approach depends on whether or not the following questions can be answered:

Fig. 2. Effects of flatness specification on wafer cost.

How are grinding marks generated? How do grinding parameters affect grinding marks? How can grinding marks be controlled? What kinds of grinding marks are easier for polishing process to remove?

Pei and Strasbaugh [20] have previously reported a 240 preliminary investigation into grinding marks. That 241 investigation covers (a) nature of grinding marks, (b) 242 factors that have effects on grinding marks, and (c) 243 approaches to reduce grinding marks. Further research 244 is needed to answer those questions presented in the pre-245 ceding paragraph. 246

## 1.6. Outline of this paper

The future of fine grinding is largely determined by 248 whether or not the polishing amount can be further 249 reduced. However, the polishing amount has to be large 250 enough to remove all grinding marks. This paper will 251 present a mathematical model on grinding marks. The 2.52 objectives are to understand the formation mechanisms 253 of grinding marks and to provide guidance to optimize 254 the grinding process for the minimum polishing amount. 255

This paper is organized into five sections. Following 256 this introduction section, Section 2 develops the math-257 ematical model. In Section 3, the model is used to predict 258 the relations between the grinding marks (the locus of 259 grinding lines and the distance between adjacent lines) 260 and the grinding parameters. Section 4 discusses the 261 pilot experiments performed to verify the model. Con-262 clusions are drawn up in Section 5. 263

## 2. Development of mathematical model

The literature most relevant to grinding marks 265 includes analyses on vertical-spindle surface grinding 266 using conventional wheels [21], diamond cup wheel 267 grinding of parabolic and toroidal surface on ceramics 268 for mirrors [22,23], and precision cylindrical face grind-260 ing using a narrow ring superabrasive wheel [24]. These 270 analyses are instrumental to the model development for 271 wafer grinding, but cannot be applied directly. 272

582

585

586

588

236

237

238

239

247

264

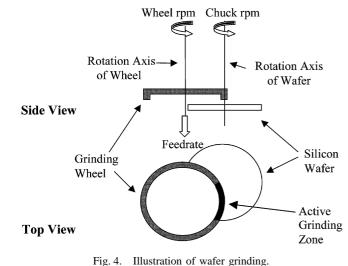

Fig. 4 illustrates the wafer grinding process. The grinding wheel shown is a diamond cup wheel. The wafer is held on the porous ceramic chuck by means of vacuum. The axis of rotation for the grinding wheel is offset by the distance of the wheel radius relative to the axis of rotation for the wafer. During grinding, the grinding wheel and the wafer rotate about their own axes of rotation simultaneously, and the wheel is fed towards the wafer along its axis of rotation.

4

273

274

275

276

278

279

280

281

282

283

28/

285

286

287

289

290

291

293

294

295

297

298

299

301

302

303

304

305

581

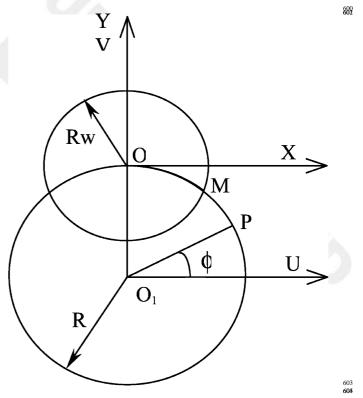

Development of the model in this paper is based on the assumption that the grinding wheel behaves like a single-point tool. This assumption has been validated by the authors' previous research [7,20] and also used by other researchers [24]. The grinding wheel removes the work material from the edge to the center along the arch MO, as shown in Fig. 5. Two coordinate systems XOY and  $UO_1V$ , are used to define all the points on the wafer and the grinding wheel. The origin of the UO<sub>1</sub>V coordinate system is at the center of the grinding wheel and the origin of the XOY coordinate system is at the center of the wafer. The  $UO_1V$  system is offset from the XOY system along the Y-axis by a distance of R, the radius of the grinding wheel. The grinding wheel revolves about its center  $O_1$  at a speed of  $N_s$  (rpm, or revolution per minute). The wafer revolves about its center O at a speed of  $N_{\rm c}$  (rpm). The radius of the wafer is  $R_{\rm w}$ .

For any point *P* with coordinates (u, v) in the UO<sub>1</sub>V system and (x, y) in the XOY system, there is the following relation.

$$\begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & -R \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} u \\ v \\ 1 \end{bmatrix}$$

(1)

The movement of the single cutting point while in contact with the wafer will generate the arc MO if the

Fig. 5. Illustration of coordinate systems.

608

wafer is stationary. The arc can be described by the following equations in the  $UO_1V$  system. 307

$$u = R \cdot \cos\phi = R \cdot \cos(2\pi \cdot N_{\rm s} \cdot t) \qquad t_1 \le t \le \frac{1}{4N_{\rm s}}$$

$$v = R \cdot \sin\phi = R \cdot \sin(2\pi \cdot N_{\rm s} \cdot t) \qquad (2) \qquad (30)$$

where,  $\phi$  is the angle between the line OP and the *U*axis, and  $t_1$  is the time it takes for point *P* to move from coordinate (*R*, 0) to point *M* along the circle with center at  $O_1$  and radius of *R*. The following equation can be used to calculate  $t_1$ .

$$t_1 = \frac{1}{2\pi N_s} \left( \frac{\pi}{2} - 2\arcsin\left(\frac{R_w}{2R}\right) \right) \tag{3}$$

Through Eq. (1), arch MO can be described in the XOY coordinate system by the following equations.

Let point *M* at the edge of the wafer be the starting point 321of the first grinding line. The coordinates of point *M* can be calculated from Eq. (4) if letting  $t = t_1$ . The starting points of subsequent grinding lines can be obtained from Eq. (4) when  $t = t_n$  where  $t_n$  is given by the following equation.

$$t_n = \frac{1}{2\pi N_{\rm s}} \left( \frac{\pi}{2} - 2\arcsin\left(\frac{R_{\rm w}}{2R}\right) \right) + \frac{n-1}{N_{\rm s}} \quad n = 2, 3, 4... \quad (5) \quad {}_{328}^{327}$$

Note that the arch MO described by Eqs. (2) or (4) is 32

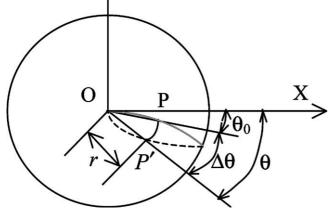

the locus of a grinding line if the wafer keeps stationary. Due to the simultaneous revolution of the wafer, point P will be offset to P' on the wafer as shown in Fig. 6. In order to get the coordinates of point P', the following parameters are necessary.

S. Chidambaram et al. / International Journal of Machine Tools & Manufacture XX (2003) XXX-XXX

$$_{335}_{336} \qquad \boldsymbol{\theta}_0 = \arctan\left(\frac{y}{x}\right) \tag{6}$$

$\Delta \theta = 2\pi \cdot N_{\rm c} \cdot (t - t_1)$ (7)338

$$_{339} \qquad \theta = \theta_0 - \Delta \theta \tag{8}$$

$$\frac{1}{342} \qquad r = \sqrt{x^2 + y^2} \tag{9}$$

Thus, the coordinates of P' can be written as (x', y'). 343

$$x' = r \cdot \cos(\theta) \tag{10}$$

The above mathematical equations are used to develop 346 a program using a commercial software package Matlab 347 (The MathWorks, Inc., 3 Apple Hill Drive, Natick, MA 348 01760, USA). This program will accept grinding para-349 meters as input variables and plot the grinding marks as 650 output. It will also calculate the distance between adjac-351 ent grinding lines. 352

#### 3. The effects of process parameters on grinding 353 marks 354

In the preceding section, a mathematical model has 355 been developed to predict the grinding marks when the 356 process parameters (i.e., wheel rotational speed, chuck 357 rotational speed, and wheel radius) are known. Next, this model will be used to investigate the effects of process 359 parameters on grinding marks. 360

Y∧

609

612

613

616

2

330

331

332

333

334

34

Fig. 6. Offset of point P to P' due to wafer rotation.

Chuck speed  $N_e$  (rpm) 55 75

2320

35

Grinding wheel speed  $N_s$  (rpm)

3400

Fig. 7. Effects of wheel speed and chuck speed on grinding marks.

## 3.1. Effects on the distance between adjacent grinding lines

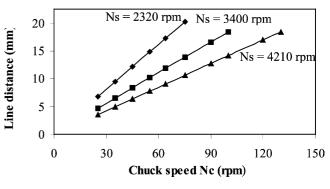

Fig. 7 shows the variation of the distance between adjacent grinding lines as wheel rotational speed and chuck speed change. It can be seen that, as chuck speed increases, the distance between adjacent grinding lines increases. Furthermore, as wheel speed increases, the line distance decreases. The above observation can also be made from Fig. 8.

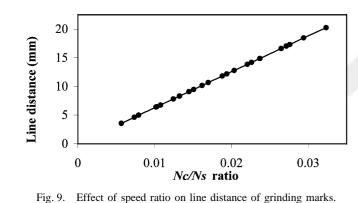

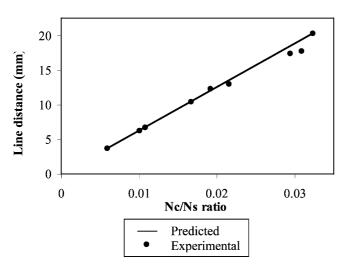

Fig. 9 shows the influence of the  $N_c/N_s$  ratio on the line distance.  $N_c$  is the chuck speed and  $N_s$  the wheel speed. An important finding is that the line distance is determined by the  $N_c/N_s$  ratio. As the speed ratio increases, the line distance increases.

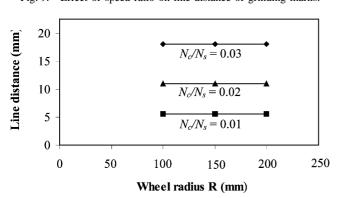

Fig. 10 shows the effects of wheel radius. It is obvious that the wheel radius has no effects on the line distance.

621 623

625

361

362

363

364

365

366

367

368

370

371

372

373

374

375

376

627

630 631

5

640 642

643

849

649

650

652

654

377

378

379

838

6

S. Chidambaram et al. / International Journal of Machine Tools & Manufacture XX (2003) XXX-XXX

Fig. 10. Effect of grinding wheel radius on line distance of grinding marks.

## 3.2. Effects on the curvature of grinding lines

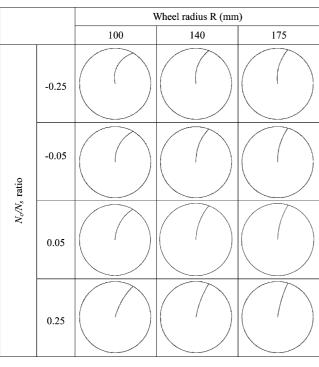

Fig. 11 shows the variation of a grinding line as wheel radius and  $N_c/N_s$  ratio change. Negative speed ratio

Fig. 11. Effects of wheel radius and speed ratio on the curvature of grinding marks.

means that the chuck rotates in the reversed direction. It can be seen that the grinding line tends to be less curved as the  $N_c/N_s$  ratio increases, or as the wheel radius increases. 383

384

385

397

398

399

400

401

402

403

404

405

420

## 4. Pilot experimental verification

## 4.1. Experimental conditions and procedures

Grinding experiments are conducted on a Strasbaugh 386 Model 7AF wafer grinder (Strasbaugh, Inc., San Luis 387 Obispo, California). The grinding wheel used is a dia-388 mond cup wheel. The grit size is mesh no. 320 for the 389 coarse grinding wheel and mesh no. 2000 for the fine-390 grinding wheel. The radius of the wheels is 140 mm. 391 Single crystal silicon wafers of 200 mm in diameter with 392 (100) plane as the major surface (the front or back sur-393 face of the wafer) are used for this investigation. Unless 394 otherwise stated, the feedrate is 1.2 µm/s, and the grit 395 size of the wheel is mesh no. 320. 396

During grinding, deionized (purified) water is used to cool the grinding wheel and the wafer surface. For this study, coolant is provided to the inner side of the cup wheel. The coolant flow rate is 3.2 gal/min.

To obtain the distance between two successive grinding lines, the number of distinctive grinding lines on the wafer is counted. Dividing the circumference of the wafer by the number of grinding lines gives the line distance.

Selected ground wafers are further polished for magic 406 mirror inspection. The purpose of this polishing oper-407 ation is to provide a shining surface for the magic mirror 408 inspection. Polishing experiments are conducted on a 409 Strasbaugh Model 6DZ wax mount polisher (Strasbaugh, 410 Inc., San Luis Obispo, California). The polishing slurry 411 used is Rodel 1540, and the polishing pad used is Suba 412 500, both are manufactured by Rodel (Phoenix, 413 Arizona). More information on the slurry and pad can 414 be found at: http://www.rodel.com. The polished wafers 415 are then inspected under a magic mirror (Model YIS-416 200SP-4, HOLOGENIX, Huntington Beach, California). 417 More information on the magic mirror technology can 418 be found in [25-27]. 419

## 4.2. Experimental results

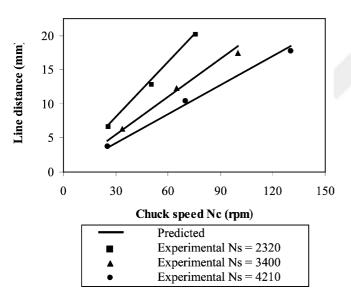

Figs. 12 and 13 show the comparison of experimental<br/>and predicted effects on the line distance of grinding<br/>marks. It can be seen that the experimental results<br/>matched very well with the predicted values.421<br/>422

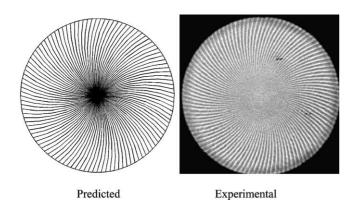

Fig. 14 shows the comparison of a magic mirror pic-<br/>ture of a ground wafer and the predicted pattern of grind-<br/>ing marks. It can be seen that both the line distance and<br/>curvature of the predicted grinding marks match well<br/>with the magic mirror picture.425420427

## ARTICLE IN PRESS

Fig. 12. Comparison of experimental and predicted effects of wheel speed and chuck speed.

Fig. 13. Comparison of experimental and predicted effects of speed ratio.

Fig. 14. Comparison of experimental and predicted grinding marks. ( $N_c$ =40 rpm,  $N_s$ =4350 rpm, feedrate=0.1  $\mu$ m s<sup>-1</sup>, grit size=#2000)

### 5. Conclusions

A mathematical model is developed to predict the line 431 distance and locus of grinding marks in wafer grinding. 432 The model predicts the following relations between the 433 grinding marks and process parameters: 434

- 1. The distance between the adjacent grinding lines is determined by the ratio of chuck speed and wheel speed. As the speed ratio increases, the line distance increases.

436

437

438

438

439

- 2. The speed ratio also affects the curvature of the grinding lines. As the speed ratio increases, the grinding lines tend to become less curved.

- 3. As the radius of the grinding wheel increases, the grinding lines tend to become less curved.

The results of pilot experiments agree well with the model predictions.

The mathematical model developed may seem simple 449 or even trivial. However, the relationship between grind-450 ing parameters and grinding marks has not been avail-451 able in literature. This model provides a powerful tool 452 to optimize grinding processes so that grinding marks 453 can be easily removed by subsequent polishing pro-454 cesses. Polishing can effectively remove high-frequency 455 surface roughness (caused by individual diamond grains 456 in the grinding wheel), but its ability to remove grinding 457 marks heavily depends on their frequency (or 458 wavelength). With this mathematical model, frequency 459 and curvature of grinding marks can be controlled by 460 selecting proper grinding parameters. This, in turn, 461 makes it possible to systematically study grinding and 462 polishing processes to eliminate grinding marks. 463

Validation of this mathematical model has further substantiated the assumption that the grinding wheel 465 behaves like a single-point cutter (due to dynamic 466 unbalance). This suggests that any measures to reduce 467 the unbalance of the grinding wheel should help reduce 468 grinding marks. 469

The mathematical model developed in this paper is 470 also applicable to other wafer grinding applications. Two 471 examples are grinding of wire-sawn wafers and grinding 472 of backsides of completed IC wafers. 473

## Acknowledgements

Financial support was provided by the Advanced 475 Manufacturing Institute of Kansas State University. 476 Also, the authors would like to thank Mr. Michael 477 Bevins at Hologenix (Huntington Beach, California) for 478 his assistance in the magic mirror inspections. 479

7

430

445

446

447

448

474

670

672

674

§79

689

692

694

ARTICLE IN PRESS

## References

8

480

481

482

483

484

485

480

487

488

489

490

491

492

493

494

495

496

497

498

499

500

501

502

503

504

505

506

507

508

509

510

511

512

513

514

515

516

517

518

519 520

521

2

- P. Van Zant, Microchip Fabrication, McGraw-Hill, New York, 2000.

- [2] M. Tricard, S. Kassir, P. Herron, Z.J. Pei, New abrasive trends in manufacturing of silicon wafers, in: Silicon Machining Symposium, American Society For Precision Engineering, St. Louis, Missouri, April, 1998.

- [3] AnoSilicon wafer shipments, revenue fell sharply in 2001, East Bay Business Times, February 12, 2002, retrieved from: http://eastbay.bizjournals.com/eastbay/.

- [4] B. Mcllvaine, A great 2000, painful 2001, and hope for next year, 2002, retrieved from: www.ebnonline.com.

- [5] M.S. Bawa, E.F. Petro, H.M. Grimes, Fracture strength of large diameter silicon wafers, Semiconductor International November (1995) 115–118.

- [6] T. Fukami, H. Masumura, K. Suzuki, H. Kudo, Method of manufacturing semiconductor mirror wafers, European Patent Application EP0782179A2, 1997.

- [7] Z.J. Pei, A study on surface grinding of 300 mm silicon wafers, International Journal of Machine Tools and Manufacture 42 (3) (2002) 385–393.

- [8] H.K. Tonshoff, W.V. Schmieden, I. Inasaki, W. Konig, G. Spur, Abrasive machining of silicon, Annals of CIRP 39 (2) (1990) 621–630.

- [9] M. Kulkarni, A. Desai, Silicon wafering process flow, US Patent 6,294,469, 2001.

- [10] H.S. Oh, H.L. Lee, A comparative study between total thickness variance and site flatness of polished silicon wafer, Japanese Journal of Applied Physics 40 (9A) (2001) 5300–5301.

- [11] K.V. Ravi, Materials quality and materials cost—are they on a collision course?, Solid State Phenomena 69-70 (1999) 103–110.

- [12] Specifications for polished mono-crystalline silicon wafers, SEMI M1-0600, Semiconductor Equipment and Materials International, San Jose, CA, 2000.

- [13] T. Kato, H. Masumura, H. Kudo, Method of manufacturing semiconductor wafers, US Patent 5,800,725, 1998.

- [14] R. Vandamme, Y. Xin, Z.J. Pei, Method of processing semiconductor wafers, US Patent 6,114,245, 2000.

- [15] Z.J. Pei, A. Strasbaugh, Fine grinding of silicon wafers, International Journal of Machine Tools and Manufacture 41 (5) (2001) 659–672.

- [16] Z.J. Pei, A. Strasbaugh, Fine grinding of silicon wafers: designed

experiments, International Journal of Machine Tools and Manufacture 42 (3) (2002) 395–404.

522

523

524

525

526

527

528

529

530

531

532

533

534

535

536

537

538

539

540

541

542

543

544

545

546

547

548

549

550

551

552

553

554

555

556

557

558

559

560

- [17] S. Chidambaram, Z.J. Pei, S. Kassir, Fine grinding of silicon wafers: a mathematical model for the chuck shape, International Journal of Machine Tools and Manufacture 43 (7) (2003) 739– 746.

- [18] H.S. Oh, S.E. Park, S.M. Jeong, S.S. Kim, H.L. Lee, Process induced mechanical damage and fine grinding process parameters, in: The Fourth International Symposium on Advances in Abrasive Technology (ISAAT'2001), November 6–9, Yonsei University, Seoul, Korea, 2001.

- [19] H. Dietrich, W. Bergholz, S. Dubbert, Three hundred-mm wafers: a technological and an economical challenge, Microelectronic Engineering 45 (1999) 183–190.

- [20] Z.J. Pei, A. Strasbaugh, Fine grinding of silicon wafers: grinding marks, in: CD-ROM Proceedings of 2002 International Mechanical Engineering Congress and Exposition (IMECE 2002), vol. 2, American Society of Mechanical Engineers, New York, 2002.

- [21] M.C. Shaw, Principles of Abrasive Processing, Oxford University Press, New York, 1996.

- [22] Z. Zhong, V.C. Venkatesh, Generation of parabolic and toroidal surfaces on silicon and silicon-based compounds using diamond cup grinding wheels, Annual of CIRP 43 (1) (1994) 323–326.

- [23] Z. Zhong, T. Nakagawa, Grinding of aspherical SiC mirrors, Journal of Materials Processing Technology 56 (1996) 37–44.

- [24] A.J. Shih, N.L. Lee, Precision cylindrical face grinding, Precision Engineering 23 (3) (1999) 177–184.

- [25] S. Hahn, K. Kugimiya, M. Yamashita, P.R. Blaustein, K. Takahashi, Characterization of mirror-like wafer surfaces using the magic mirror method, Journal of Crystal Growth 103 (1-4) (1990) 423–432.

- [26] S. Hahn, K. Kugimiya, K. Vojtechovsky, M. Sifalda, M. Yamashita, P.R. Blaustein, K. Takahashi, Characterization of mirror-polished Si wafers and advanced Si substrate structures using the magic mirror method, Semiconductor Science and Technology 7 (1A) (1992) 80–85.

- [27] C.C. Shiue, K.H. Lie, P.R. Blaustein, Characterisation of deformations and texture defects on polished wafers of III–V compound crystals by the magic mirror method, Semiconductor Science and Technology 7 (1A) (1992) 95–97.